计算机组成原理-Part4

计算机组成原理-Part4——指令系统

[TOC]

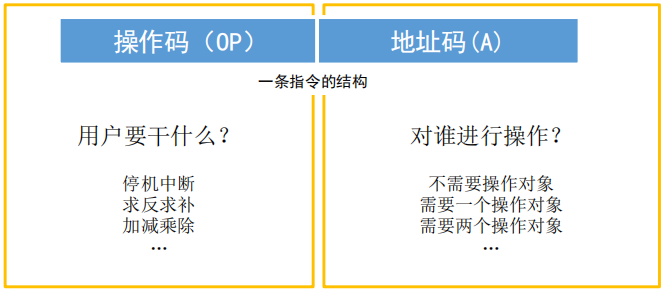

指令格式

指令

- 指令(机器指令):一台计算机的所有指令的集合构成该机的指令系统,也称为指令集。

- 一台计算机只能执行自己指令系统中的指令,不能执行其他系统的指令。Eg:x86 架构、ARM架构

根据地址码数目不同分类

- 一条指令可能包含不同数量的地址码

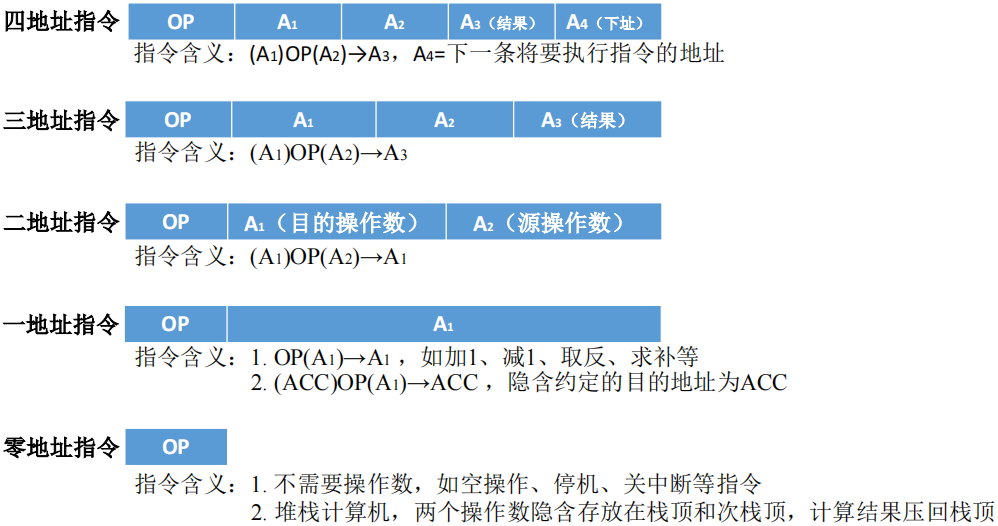

- 零地址指令

- 不需要操作数,如空操作、停机、关中断等指令

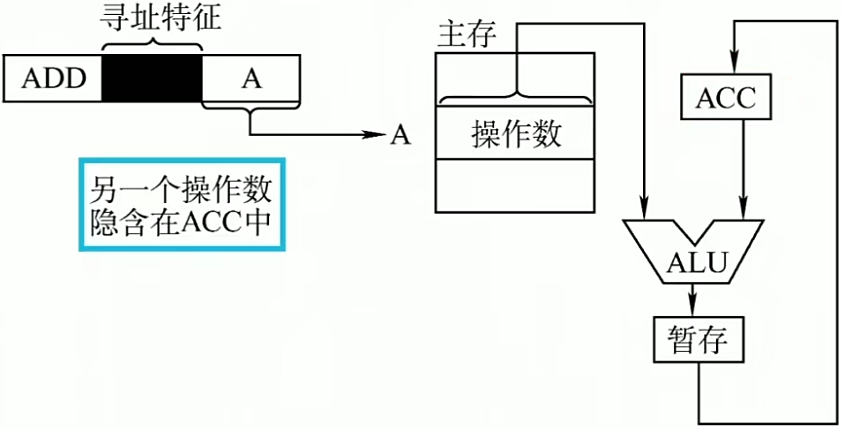

- 一地址指令

- 只需要单操作数,如加1、减1、取反、求补等

- 指令含义:OP(A1) -> A1 ,完成一条指令需要 3 次访存:取指 -> 读A1 -> 写A1

- 需要两个操作数,但其中一个操作数隐含在某个寄存器(如隐含在ACC)

- 指令含义: (ACC)OP(A1) -> ACC,完成一条指令需要2次访存:取指 -> 读A1

- 注:A1 指某个主存地址, (A1)表示 A1 所指向的地址中的内容

- 只需要单操作数,如加1、减1、取反、求补等

- 二地址指令

- 常用于需要两个操作数的算术运算、逻辑运算相关指令

- 指令含义:(A1)OP(A2) -> A1

- 完成一条指令需要访存 4 次,取指 -> 读A1 -> 读A2 -> 写A1

- 三地址指令

- 常用于需要两个操作数的算术运算、逻辑运算相关指令

- 指令含义:(A1)OP(A2) -> A3

- 完成一条指令需要访存 4 次,取指 -> 读A1 -> 读A2 -> 写A3

- 四地址指令

- 指令含义:(A1)OP(A2) -> A3,A4=下一条将要执行指令的地址

- 完成一条指令需要访存 4 次,取指 -> 读A1 -> 读A2 -> 写A3

- 若指令总长度固定不变,则地址码数量越多,寻址能力越差

根据指令长度分类

- 指令字长:一条指令的总长度(可能会变)

- 机器字长:CPU进行一次整数运算所能处理的二进制数据的位数(通常和ALU直接相关)

- 存储字长:一个存储单元中的二进制代码位数(通常和MDR位数相同)

- 半字长指令、单字长指令、双字长指令——指令长度是机器字长的 n 倍

- 指令字长会影响取指令所需时间。如:机器字长=存储字长=16bit,则取一条双字长指令需要两次访存

- 定长指令字结构:指令系统中所有指令的长度都相等

- 变长指令字结构:指令系统中各种指令的长度不等

根据操作码长度分类

- 定长操作码:指令系统中所有指令的操作码长度都相同

- 控制器的译码电路设计简单,但灵活性较低

- n 位 -> 2^n^ 条指令

- 优:定长操作码对于简化计算机硬件设计,提高指令译码和识别速度很有利;

- 缺:指令数量增加时会占用更多固定位,留给表示操作数地址的位数受限。

- 可变长操作码:指令系统中各指令的操作码长度可变

- 控制器的译码电路设计复杂, 但灵活性较高

- 不同地址数的指令可以具有不同长度的操作码,从而在满足需要的前提下,有效地缩短指令字长。

- 优: 在指令字长有限的前提下仍保持比较丰富的指令种类;

- 缺 :增加了指令译码和分析的难度,使控制器的设计复杂化。

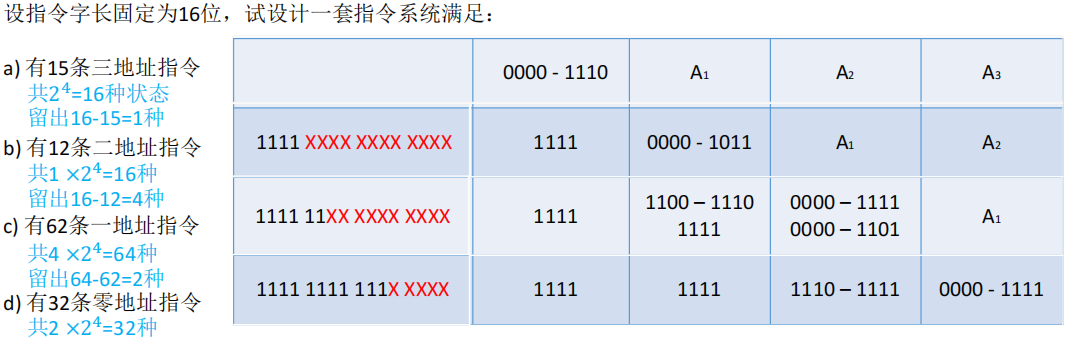

- 定长指令字结构+可变长操作码 -> 扩展操作码指令格式

- 不同地址数的指令使用不同长度的操作码

根据操作类型分类

- 数据传送类:进行主存与CPU之间的数据传送

- 数据传送

- LOAD:把存储器中的数据放到寄存器中

- STORE:把寄存器中的数据放到存储器中

- 数据传送

- 运算类

- 算术逻辑操作

- 算术:加、减、乘、除、增 1、减 1、求补、浮点运算、十进制运算

- 逻辑:与、或、非、异或、位操作、位测试、位清除、位求反

- 移位操作

- 算术移位、逻辑移位、循环移位(带进位和不带进位)

- 算术逻辑操作

- 程序控制类:改变程序执行的顺序

- 转移操作

- 无条件转移 JMP

- 条件转移 JZ:结果为 0;JO:结果溢出;JC:结果有进位

- 调用和返回 CALL 和 RETURN

- 陷阱(Trap)与陷阱指令

- 转移操作

- 输入输出类(I/O):进行CPU和I/O设备之间的数据传送

- 输入输出操作

- CPU 寄存器与 IO 端口之间的数据传送(端口即 IO 接口中的寄存器)

- 输入输出操作

扩展操作码指令格式

- 扩展操作码:定长指令字结构+可变长操作码

- 设计扩展操作码指令格式的注意点:

- 不允许短码是长码的前缀。

- 各指令的操作码一定不能重复。

- 通常情况下,对使用频率较高的指令,分配较短的操作码;对使用频率较低的指令,分配较长的操作码。从而尽可能减少指令译码和分析的时间。

- 设地址长度为 n,上一层留出 m 种状态,则下一层可扩展出 m×2^n^ 种状态

指令寻址

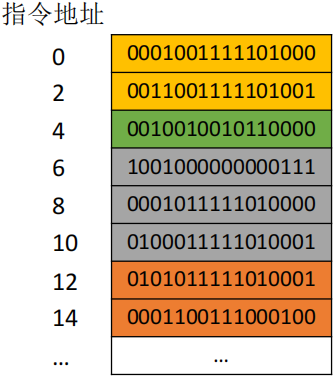

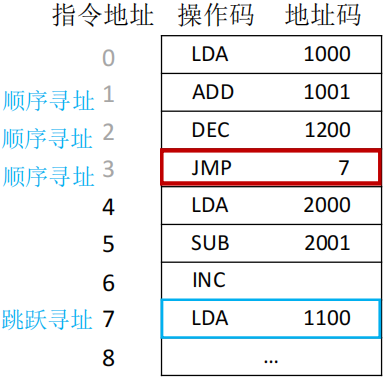

顺序寻址

- 指令寻址:下一条欲执行指令的地址(始终由程序计数器PC给出)

- 顺序寻址:( PC ) + “1” -> PC

- 这里的“1”理解为 1 个指令的字长,实际加的值会因指令长度、编址方式而不同

- 定长指令字结构 + 按字编址 + 指令字长=存储字长=16bit=2B:每次 PC + 1

- 定长指令字结构 + 按字节编址 + 指令字长=存储字长=16bit=2B:每次 PC + 2

- 变长指令字结构 + 按字节编址 + 指令字长!=存储字长=16bit=2B:每次 PC + n

- 根据指令的类型,CPU 可能还要进行多次访存,每次读入一个字

跳跃寻址

- 跳跃寻址:由转移指令指出

- CPU 与 PC 之间的顺序:

- CPU 取出 PC 中存储的指令

- PC += 1

- CPU 执行取出的指令

- 如果是执行转移指令,则修改 PC 内容

- CPU 取出 PC 中存储的指令。Loop

- 每一条指令的执行都分为 “取指令”、“执行指令” 两个阶段

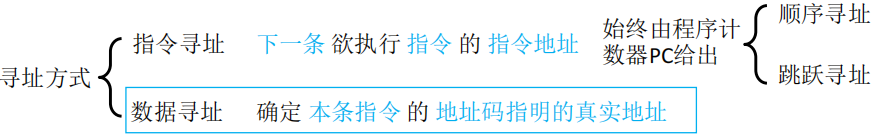

数据寻址

指令寻址 v.s. 数据寻址

- 求出操作数的真实地址,称为有效地址(EA)。

直接与间接寻址

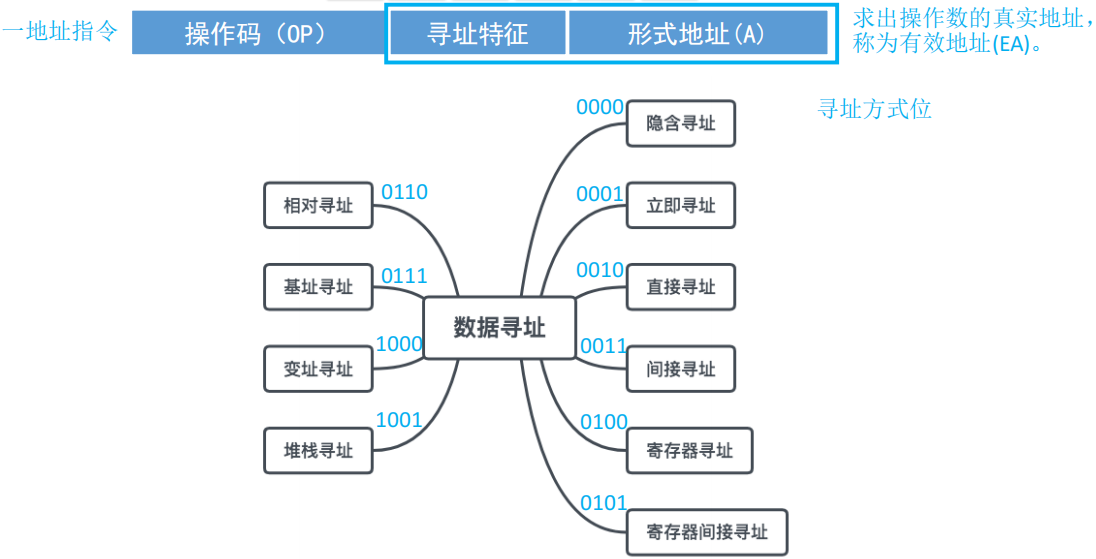

直接寻址

- 直接寻址:指令字中的形式地址 A 就是操作数的真实地址 EA(effective address)**,即 **EA=A 。

- 共访存 2 次:取指令访存1次;执行指令访存 1 次。

- 优点:

- 简单,指令执行阶段仅访问一次主存,不需专门计算操作数的地址。

- 缺点:

- A 的位数决定了该指令操作数的寻址范围。

- 操作数的地址不易修改。

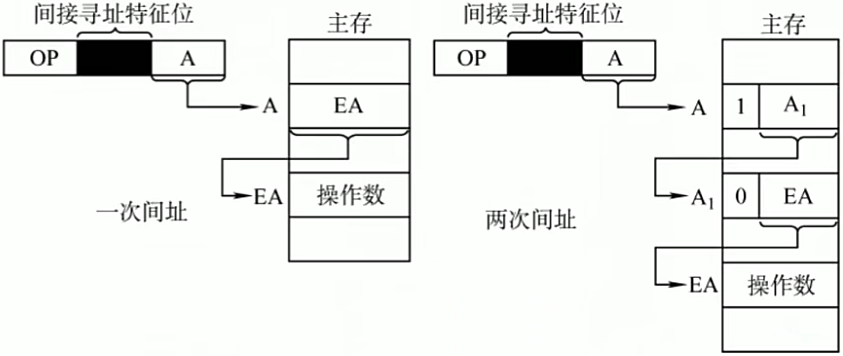

间接寻址

- 间接寻址:指令的地址字段给出的形式地址是操作数有效地址所在的存储单元的地址,也就是操作数地址的地址,即 EA=(A) 。

- 共访存 3 次:取指令访存 1 次;执行指令访存 2 次。

- 优点:

- 可扩大寻址范围(有效地址 EA 的位数大于形式地址 A 的位数)。

- 便于编制程序(用间接寻址可以方便地完成子程序返回)。

- 缺点:

- 指令在执行阶段要多次访存(一次间址需两次访存,多次寻址需根据存储字的最高位确定几次访存)。

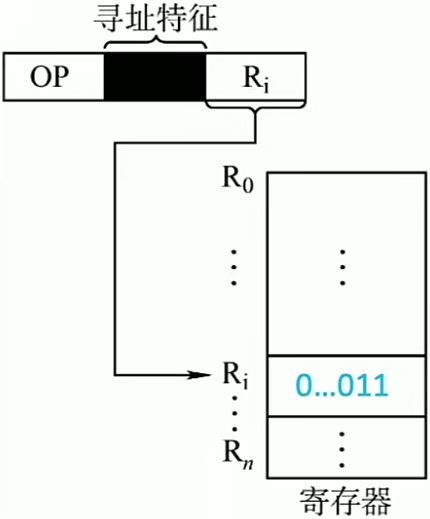

寄存器寻址

- 寄存器寻址:在指令字中直接给出操作数所在的寄存器编号,即 **EA=R

i**,其操作数在由 Ri所指的寄存器内。 - 共访存 1 次:取指令访存 1 次;执行指令访存 0 次。

- 优点:

- 指令在执行阶段不访问主存,只访问寄存器

- 指令字短且执行速度快,支持向量/矩阵运算。

- 缺点:

- 寄存器价格昂贵,计算机中寄存器个数有限 。

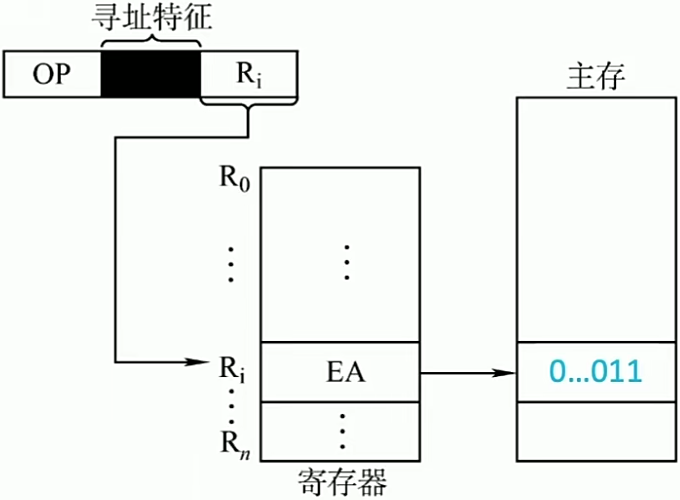

寄存器间接寻址

- 寄存器间接寻址:寄存器 R

i中给出的不是一个操作数,而是操作数所在主存单元的地址,即 EA=(Ri) 。 - 共访存 2 次:取指令访存 1 次;执行指令访存 1 次。

- 特点:

- 与一般间接寻址相比速度更快,但指令的执行阶段需要访问主存(因为操作数在主存中)。

隐含寻址

- 隐含寻址:不是明显地给出操作数的地址,而是在指令中隐含着操作数的地址。

- 共访存 1 次:取指令访存 1 次;执行指令访存 0 次。

- 优点:有利于缩短指令字长。

- 缺点:需增加存储操作数或隐含地址的硬件。

立即寻址

- 立即寻址:形式地址 A 就是操作数本身,又称为立即数,一般采用补码形式。“#”表示立即寻址特征。

- 共访存 1 次:取指令访存 1 次;执行指令访存 0 次。

- 优点:指令执行阶段不访问主存,指令执行时间最短

- 缺点:A 的位数限制了立即数的范围。

- 如 A 的位数为 n,且立即数采用补码时,可表示的数据范围为:−2^n-1^ ~ 2^n-1^−1

偏移寻址

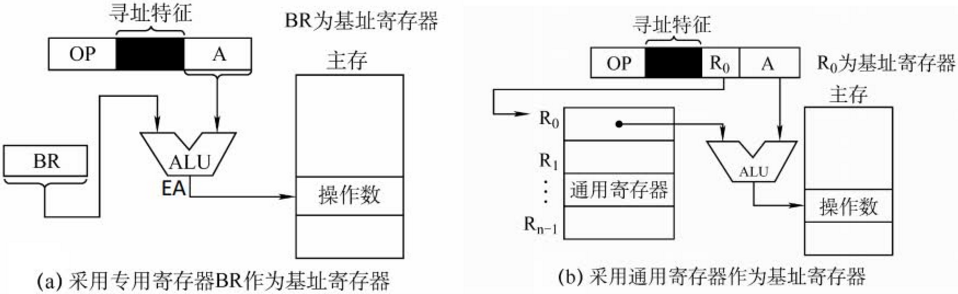

基址寻址(多道程序)

- 基址寻址:将 CPU 中基址寄存器(base address register,BR)的内容加上指令格式中的形式地址 A,而形成操作数的有效地址,即 EA=(BR)+A。

- 操作系统第三章第一节学习,OS 课中的“重定位寄存器”就是“基址寄存器”

- 程序运行前,CPU 将 BR 的值修改为该程序的起始地址(存在操作系统 PCB 中)

- 基址寄存器是面向操作系统的,其内容仅由操作系统或管理程序确定,对于程序员是透明的。

- 基址寄存器的内容不变(作为基地址),形式地址可变(作为偏移量)。

- 当采用通用寄存器作为基址寄存器时,可由用户决定哪个寄存器作为基址寄存器,但其内容仍由操作系统确定。

- 优点:

- 便于程序在内存里的地址浮动,方便实现多道程序并发运行

- 可扩大寻址范围(基址寄存器的位数大于形式地址的位数)

- 用户不必考虑自己的程序存于主存的哪一空间区域,故有利于多道程序设计

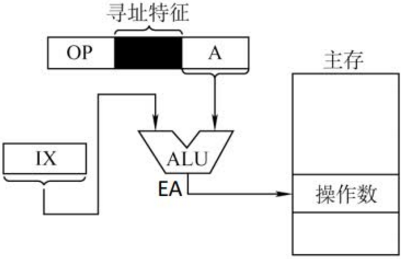

变址寻址(循环程序)

- 变址寻址:有效地址 EA 等于指令字中的形式地址 A 与变址寄存器 IX 的内容相加之和,即 EA=(IX)+A。其中 IX 可为变址寄存器(专用),也可用通用寄存器作为变址寄存器。

- 变址寄存器是面向用户的,变址寄存器的内容可由用户改变

- 基址寄存器的内容不变(作为偏移量),形式地址可变(作为基地址)。

- 优点:

- 在数组处理过程中,可设定 A 为数组的首地址,不断改变变址寄存器 IX(index register) 的内容,便可很容易地表示数组中任一数据的地址,适合编制循环程序。

- 两者同样可以一起使用——基址&变址复合寻址

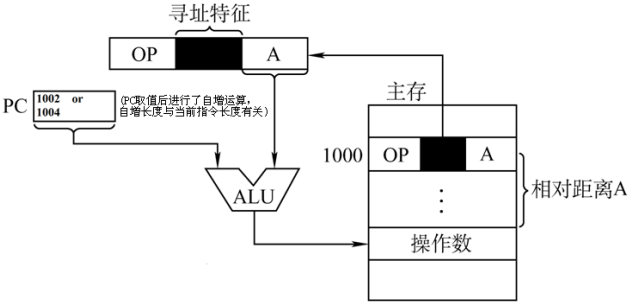

相对寻址(转移指令)

- 相对寻址:把程序计数器 PC 的内容加上指令格式中的形式地址 A 而形成操作数的有效地址,即 EA=(PC)+A。

- A 是相对于下一条指令(PC 所指地址)的偏移量,可正可负,补码表示 。因为 PC 会在取出指令后立刻加一。

- 优点:

- 便于一段代码在程序内部的浮动。

- 相对寻址广泛应用于转移指令。

堆栈寻址

堆栈寻址

- 堆栈寻址:操作数存放在堆栈中,隐含使用堆栈指针(Stack Pointer, SP)作为操作数地址。

- 堆栈是一块按“后进先出(LIFO)”原则管理的存储区,该存储区中被读/写单元的地址是用堆栈指针给出的。

- 堆栈可以由寄存器组(硬堆栈,成本高)或者主存中划分一块区域(软堆栈,成本低)实现。

- 有堆栈才可以方便地实现保护现场、调用函数。

数据寻址总结

| 寻址方式 | 有效地址 | 访存次数(指令执行期间) |

|---|---|---|

| 直接寻址 | EA=A | 1 |

| 一次间接寻址 | EA=(A) | 2 |

| 寄存器寻址 | EA=R |

0 |

| 寄存器间接一次寻址 | EA=(R |

1 |

| 隐含寻址 | 程序指定 | 0 |

| 立即寻址 | A 即是操作数 | 0 |

| 基址寻址 | EA=(BR)+A | 1 |

| 变址寻址 | EA=(IX)+A | 1 |

| 相对寻址 | EA=(PC)+A | 1 |

| 堆栈寻址 | 入栈/出栈时 EA 的确定方式不同 | 硬堆栈不访存,软堆栈访存1次 |

CISC 和 RISC

- CISC:Complex Instruction Set Computer

- 设计思路:一条指令完成一个复杂的基本功能。

- RISC:Reduced Instruction Set Computer

- 设计思路:一条指令完成一个基本“动作”;多条指令组合完成一个复杂的基本功能。

| 对比项目 | CISC | RISC |

|---|---|---|

| 指令系统 | 复杂 | 简单 |

| 代表 | x86 架构 | ARM 架构 |

| 指令数目 | 一般大于 200 条 | 一般小于 100 条 |

| 指令字长 | 不固定 | 定长 |

| 可访存指令 | 不加限制 | 有 Load/Store 指令 |

| 各指令执行时间 | 相差较大 | 大部分在一个周期内 |

| 各指令执行频率 | 相差较大 | 都比较常用 |

| 通用寄存器数量 | 较少 | 多 |

| 目标代码 | 难以用优化编译提高程序效率 | 可以用优化编译提高程序效率 |

| 控制方式 | 大部分为微程序控制(更慢) | 大部分为组合逻辑控制(更快) |

| 指令流水线 | 可以实现 | 必须实现 |

本博客所有文章除特别声明外,均采用 CC BY-NC-SA 4.0 许可协议。转载请注明来自 浅幽丶奈芙莲的个人博客!